Download from Dreamstime.com This watermarked comp image is for previewing purposes only D 35103813 C Yulia Gapeenko | Dreamstime.com

6

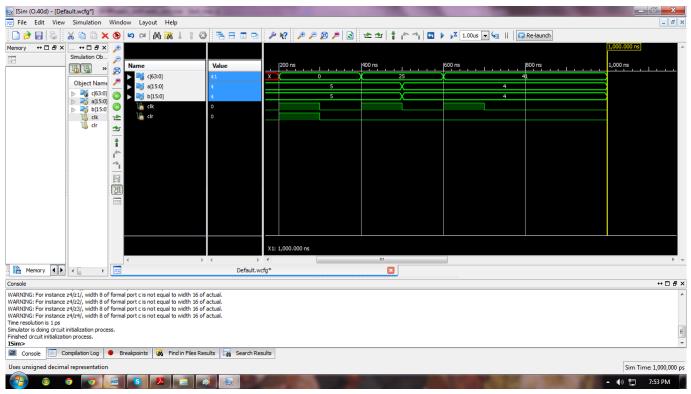

Design And Synthesis Of Alu Using Reversible Logic For Mac

| Pite Lati View Simulation Window Layout Help   Pite Lati View Simulation Window Layout Help Pite Lati View Simulation Window Layout Help Pite Lati View Simulation Charles (1) Pite Pite Lati View Simulation Charles (1) Pite Lati Vie                                                                                                                                                                                                                                                                                                                                            | 🔜 ISim (O.40d) - [Default                                                                                                                                                                             | t wcfo*]                                                                                           | and and and the                                                                                                                                                                                                                                                                                    | and the second little                                                      |                  |                                         |                   | _                    |           | _ 0 <mark></mark> ×_  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------|-----------------------------------------|-------------------|----------------------|-----------|-----------------------|

| Image: Control of the second back of th                              |                                                                                                                                                                                                       |                                                                                                    | Vindow Lavout He                                                                                                                                                                                                                                                                                   | alp                                                                        |                  |                                         |                   |                      |           |                       |

| Memory Image: Construct of the start                    |                                                                                                                                                                                                       |                                                                                                    |                                                                                                                                                                                                                                                                                                    |                                                                            | A 12             | e 🕫 🔎 📄                                 | 16 AT 1 1 16 A 16 | ▶ x 1.00us ▼ 🔙    [C | Re-launch |                       |

| X1: 1,000.000 ns         X1: 1,000.000 ns         Image: Console         VARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.         WARNING: For instance ±/s1/2, width 8 of formal port c is not equal to width 16 of actual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Memory ↔ □ ♂ ×                                                                                                                                                                                        |                                                                                                    | P       Name         20       > ■       c(63:0)         > ■       ≤(15:0)       >         30       > ■       b(15:0)         30       ■       c(k)         10       ■       c(k)         11       C(r)       ■         11       ■       C(r)         21       ■       □         21       ■       □ | Value<br>41<br>4<br>4<br>0                                                 | 200 ns           | ·   · · · · · · · · · · · · · · · · · · | 400 ns            | 600 ns               |           |                       |

| Console          |                                                                                                                                                                                                       |                                                                                                    |                                                                                                                                                                                                                                                                                                    |                                                                            | X1: 1,000.000 ns |                                         |                   |                      |           |                       |

| WARNING: For instance z4/z1/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z2/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z4/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z4/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z4/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z4/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z4/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z4/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z4/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z4/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z4/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z4/, width 8 of formal port c is not equal to width 16 of actual. WARNING: For instance z4/z4/, width 8 of formal port c is not equal to width 16 of actual. The resolution is 1 ps Simulator is doing cruit initialization process. Similar C = Similar C |                                                                                                                                                                                                       | -                                                                                                  |                                                                                                                                                                                                                                                                                                    | ► <b>←</b> ►                                                               | •                |                                         |                   |                      |           | 4                     |

| VARNING: For instance 24/z1/, width 8 of formal port c is not equal to width 16 of actual.<br>VARNING: For instance 24/21, width 8 of formal port c is not equal to width 16 of actual.<br>VARNING: For instance 24/24, width 8 of formal port c is not equal to width 16 of actual.<br>VARNING: For instance 24/24, width 8 of formal port c is not equal to width 16 of actual.<br>VARNING: For instance 24/24, width 8 of formal port c is not equal to width 16 of actual.<br>VARNING: For instance 24/24, width 8 of formal port c is not equal to width 16 of actual.<br>VARNING: For instance 24/24, width 8 of formal port c is not equal to width 16 of actual.<br>VARNING: For instance 24/24, width 8 of formal port c is not equal to width 16 of actual.<br>Simple dirout initialization process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Memory ()                                                                                                                                                                                             |                                                                                                    | 202                                                                                                                                                                                                                                                                                                | Default.wcf                                                                | g*               |                                         | ×                 |                      |           |                       |

| VARNING: For instance +/2/2, width 8 of formal port c is not equal to width 16 of actual.<br>VARNING: For instance +/2/2, width 8 of formal port c is not equal to width 16 of actual.<br>VARNING: For instance z-4/2,4/, width 8 of formal port c is not equal to width 16 of actual.<br>Imalator is doing: Coract initialization process.<br>Imalator is doing: Smp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | onsole                                                                                                                                                                                                |                                                                                                    |                                                                                                                                                                                                                                                                                                    |                                                                            |                  |                                         |                   |                      |           | +□8                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | WARNING: For instance z4/z<br>WARNING: For instance z4/z<br>WARNING: For instance z4/z<br>Time resolution is 1 ps<br>Simulator is doing circuit initial<br>Finished circuit initialization p<br>ISim> | (z2), width 8 of fi<br>(z3), width 8 of fi<br>(z4), width 8 of fi<br>alization process<br>process. | ormal port c is not equal t<br>ormal port c is not equal<br>ormal port c is not equal t<br>ormal port c is not equal t                                                                                                                                                                             | to width 16 of actual.<br>to width 16 of actual.<br>to width 16 of actual. | Its              |                                         |                   |                      |           | Ĩ                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                       |                                                                                                    |                                                                                                                                                                                                                                                                                                    | ind in Files Results Em Search Resu                                        |                  |                                         |                   |                      |           | a: T: 4 0             |

| Uses unsigned decimal representation Sim Time: 1,000,00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Uses unsigned decimal re                                                                                                                                                                              | epresentation                                                                                      |                                                                                                                                                                                                                                                                                                    |                                                                            |                  |                                         |                   |                      |           | Sim Time: 1,000,000 p |

Design And Synthesis Of Alu Using Reversible Logic For Mac

Download from Dreamstime.com This watermarked comp image is for previewing purposes only. 35103813

Yulia Gapeenko | Dreamstime.com

) The shifting and rotating tasks are also done through the ALU 3 Verilog for Simulation and Synthesis This chapter presents Verilog from the point of view of a designer wanting to describe a design, perform pre-synthesis simulation, and synthesize his or her.. [] This is so because reversible computation does not require erasing any bit of information.

COST-EFFECTIVE DESIGN OF REVERSIBLE LOGIC GATES AND ITS INDUSTRIAL APPLICATIONS Presented designed by AMITH BHONSLE Masters of Technology [VLSI Design] VTU,Belgaum.

## Formatear Un USB Para Mac En Un PC Usando DiskPart

Reversible computation does not require erasing any bit of information Consequently, it does not dissipate any energy for computation.. • With miniaturization it faces two issues i) A considerable amount of energy gets dissipated in VLSI circuits.. It performs the arithmetic operations (addition and subtraction) and logic operations (AND, OR, XOR etc.. Abstract: In low power circuit design, reversible computing has become one of the most efficient and prominent techniques in recent years. Mac Os 10.12 2 Download

download film fast and furious 8 ukuran kecil dibawah 100 mb to gb

## Best Small All In One Printer For Mac

$\square$  Voltage-coded logic signals have energy of Esig =  $\frac{1}{2}$ CV2, and this energy gets dissipated whenever switching occurs in conventional (irreversible) logic implemented in modern CMOS technology. <u>Muat Turun Adobe Photoshop Percuma Blogspot</u> Build Español A Ingles

## Cocoamysql A Mysql Gui For Mac

In this paper, two The arithmetic logic unit (ALU) is an essential part of computer processor.. Heat dissipation in the circuit has become the critical limiting factor 🛛Rolf Landauer introduced that losing of bit in circuits causes the smallest amount of heat in computation and the theoretical limit of energy dissipation for losing of one bit computation is KTln2 🖾 Even C.. • INTRODUCTION 🖾 Designing of a complex digital system which dissipates low power is a competitive topic in the research field of hardware design. 🖾 The amount of energy dissipated in a system bears a direct relationship to the number of bits erased during computation. H Bennett in 1973 also showed that the dissipated energy directly correlated to the number of lost bits • 🖾 kTln2 energy dissipation would not occur, if a computation is carried out in a reversible way.. In this paper, reversible Arithmetic and Logic Unit (ALU) is designed to show its major implications on the Central Processing Unit (CPU).. 14 2 and synthesis is done using Design And Synthesis Of Alu Using Reversible Logic For MacIeee project reversible logic gates by\_amit • 1.. Matias tactile pro keyboard for mac Ii) The size of the transistors are approaching quantum limits where tunnelling and other quantum phenomena are likely to appear.. 🖾 These circuits can generate unique output vector from each input vector, and vice versa, that is, there is a one-to-one mapping between input and output vectors... 🖾 Reversible circuits are of high interest in low-power CMOS design, optical computing, quantum computing and nanotechnology. ceal14251b Best Program For Slideshow On Mac

## cea114251b

Catia v5 64 bit herunterladen download catia v5 64 bit